Key Dates

Paper/Poster Submission Deadline

Friday January 24, 2014, 11:59.59 PM (PST)

Author Notification

Friday February 28, 2014

Camera-Ready Papers Due

Friday March 28, 2014

Submission

Submit your paper

here

Sponsors

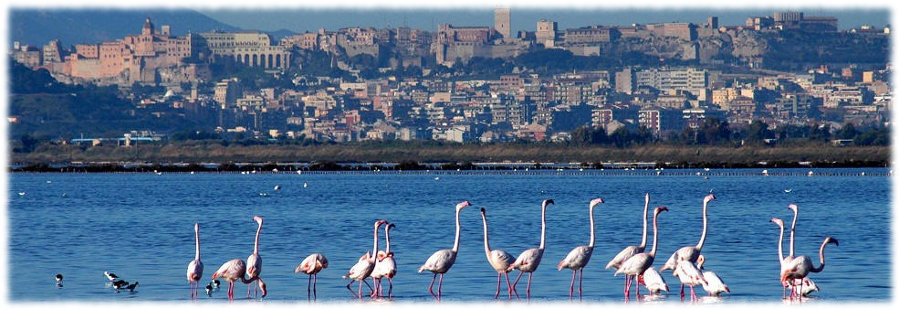

General Chair

Pedro Trancoso

University of Cyprus, CY

Program Chairs

Diana Franklin

UCSB, US

Sally A. McKee

Chalmers, SE

For more information,

visit the website at

www.computingfrontiers.org

Computing Frontiers 2014 is proud to announce the following keynote

speakers and talks this year:

- Keynote 1:

Bruce Jacob

High-Bandwidth, High-Capacity, Low-Power Memory Systems

- Keynote 2:

Gabriel Loh

Evolutionary Paths to Revolutionary Frontiers

- Keynote 3:

David Bailey

Fooling the Masses: Reproducibility in High-Performance Computing

Fooling the Masses: Reproducibility in High-Performance Computing

David Bailey, Research Fellow at University of California, Davis, US

David Bailey, Research Fellow at University of California, Davis, US

Abstract:

Reproducibility is emerging as a major issue for highly parallel

computing, in much the same way (and for many of the same reasons) that

it is emerging as an issue in other fields of science, technology and

medicine, namely the growing numbers of cases where other researchers

cannot reproduce published results. This talk will summarize a number

of these issues, including the need to carefully document computational

experiments, the growing concern over numerical reproducibility and,

once again, the need for responsible reporting of performance. Have we

learned the lessons of history?

Bio:

David Bailey is mathematician / computer scientist with the Lawrence

Berkeley Laboratory in Berkeley, California, and also a Research Fellow at

the University of California, Davis. He has authored more than

170 technical papers, five books, and numerous blog columns and

commentaries. He recently retired from the Berkeley Lab, but continues as

an active researcher.

Evolutionary Paths to Revolutionary Frontiers

Gabriel Loh, Fellow Design Engineer in AMD Research, US

Gabriel Loh, Fellow Design Engineer in AMD Research, US

Abstract:

Academic researchers often find themselves in a conundrum between doing

high-risk, forward-looking research and trying to have more immediate

impact on real-world problems. In fact, many in industry (perhaps myself

included) are guilty of telling researchers to go look ahead and tell us

what the future holds and what industry should do, and then when the

researchers come back with stunning visions of the future, we respond with

comments like "that's not practical" or "that's not how we do things today".

In this talk, I will draw on some of my experiences as both a university

professor as well as a researcher in industry, and discuss some computing

revolutions and how academic research plays a central and critical role.

As an example, I will use the on-going revolution in die-stacking

technologies to describe my view of how forward-looking visions combined

with evolutionary steps have gotten us to where we are today, why we

haven't gotten here sooner, and why some may want further delays. I will

also discuss other revolutions that are either underway or lurking in the

future. From all this, despite the near-term value of incremental

near-term innovations to industry, I will build a case for academic

researchers to continue thinking big and to push the frontiers of computing.

Bio:

Gabriel H. Loh is a Fellow Design Engineer in AMD Research, the research

and advanced development lab for Advanced Micro Devices, Inc. Gabe

received his Ph.D. and M.S. in computer science from Yale University in

2002 and 1999, respectively, and his B.Eng. in electrical engineering from

the Cooper Union in 1998. Gabe was also a tenured associate professor in

the College of Computing at the Georgia Institute of Technology, a visiting

researcher at Microsoft Research, and a senior researcher at Intel

Corporation. He is a senior member of IEEE and the ACM, (co-)inventor on

over fifty US patent applications, and a recipient of the US National

Science Foundation Young Faculty CAREER Award. His interests include

computer architecture, processor microarchitecture, memory systems,

emerging technologies, 3D die stacking, sushi, BBQ, ice hockey,

snowboarding, and mud running.

High-Bandwidth, High-Capacity, Low-Power Memory Systems

Bruce Jacob, Professor at University of Maryland, US

Bruce Jacob, Professor at University of Maryland, US

Abstract:

In large systems, scale is determined by the memory needed: users of

supercomputers choose the number of nodes based on the amount of DRAM

they will receive; administrators in data centers and enterprise computing

run the largest workload possible before paging makes performance

unacceptable. These systems are not compute-bound; they are memory-bound.

This talk will discuss several of the recent solutions that our group has

helped to develop, including flash-based main memory systems and

Micron's Hybrid Memory Cube DRAM.

Bio:

Bruce Jacob is a Full Professor and former Director of Computer Engineering

in the Dept. of Electrical and Computer Engineering at the University of

Maryland, College Park. He received his Ars Baccalaureate, cum laude, in

Mathematics from Harvard University in 1988, and his M.S. and Ph.D. in

Computer Science and Engineering from the University of Michigan in 1995

and 1997, respectively. In addition to his academic credentials, he has

extensive experience in industry: he designed real-time embedded applications

and real-time embedded architectures in the area of telecommunications for

two successful Boston-area startup companies, Boston Technology (now part

of Comverse Technology) and Priority Call Management (now part of uReach

Technologies). At Priority Call Management he was employee number 2, the

system architect, and the chief engineer; he built the first working

prototype of the company's product, and he built and installed the first

actual product as well.

In recognition of Prof. Jacob's research program, he has been honored

several times as a University of Maryland "Rainmaker." In memory-systems

research, Jacob's cache and memory-management designs in Michigan's PUMA

processor demonstrated the viability of software-managed caches in

general-purpose systems (he coined the now-common term

"software-managed cache" in his 1998 ASPLOS paper, "A look at several

memory management units, TLB-refill mechanisms, and page table

organizations"). His work in advanced DRAM architectures at Maryland is the

first comparative evaluation of today's memory technologies, and he received

the prestigious CAREER Award from the National Science Foundation for his

early work in that area. Honors for his teaching include the departmental

George Corcoran Award, the University of Maryland Award for Teaching

Excellence, and his 2006 induction as a Clark School of Engineering Keystone

Professor. He has published over 50 papers on a wide range of topics,

including computer architecture and memory systems, low-power embedded

systems, electromagnetic interference and circuit integrity, distributed

computing, astrophysics, and algorithmic composition. His recently published

book on computer memory systems (Jacob, Ng, and Wang: Memory Systems --

Cache, DRAM, Disk, Morgan Kaufmann Publishers, Fall 2007) is large enough

to choke a small elephant.

David Bailey, Research Fellow at University of California, Davis, US

David Bailey, Research Fellow at University of California, Davis, US

Gabriel Loh, Fellow Design Engineer in AMD Research, US

Gabriel Loh, Fellow Design Engineer in AMD Research, US

Bruce Jacob, Professor at University of Maryland, US

Bruce Jacob, Professor at University of Maryland, US